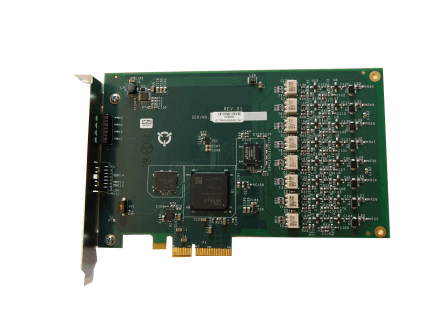

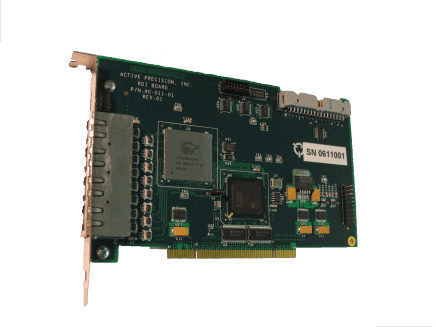

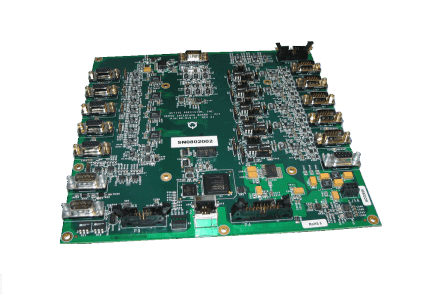

Remote I/O Cards

Verien has designed a number of remote I/O cards for different clients and applications. These cards take in slower I/O, encapsulate the I/O into packet data, and send it across an optical link at gigabit speed to the second card where the I/O is replicated. These are generally designed with a custom link protocol as it is minimizes development costs over the use of a standardized interface. The high-speed transceivers in the Xilinx Artix-7 or Altera (Intel) Cyclone V families provide a cost effective solution. The slower I/O can include a number of different types of sources and destinations: UART serial I/O, A/D, D/A, SPI, general purpose I/O, relay I/O, and others.